# Optimizing 6x86-Based Systems Using PUZZLE.EXE

# Application Note

Author: Jack Smith

Revision Summary: This is the initial release of this application note.

**Caution:** In all cases you should consult the table of required settings in the IBM 6x86 BIOS Writer's Guide and the errata notice that applies to your hardware revision level before enabling or disabling any performance related features.

This application note describes how to help optimize a system containing the IBM 6x86 processor using the PUZZLE benchmark. PUZZLE is a DOS benchmark written by IBM Microelectronics to measure the performance of the processor core.

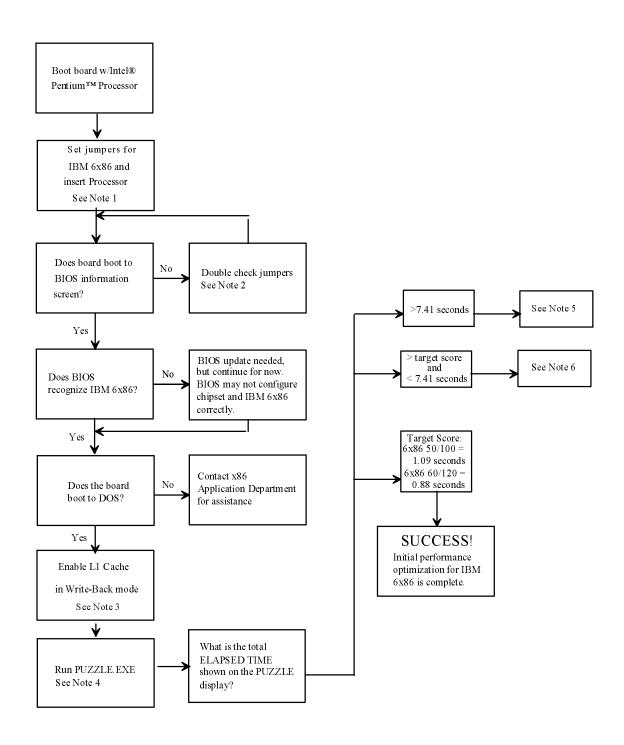

The flowchart on the following page shows the steps to help optimize PUZZLE on 6x86. It consists of four simple actions:

- 1. Boot system with an Intel Pentium processor

- 2. Change jumper settings and boot with IBM 6x86

- 3. Enable L1 cache in write-back mode

- 4. Run PUZZLE.EXE and verify score.

Once PUZZLE is optimized on 6x86, the next step is to optimize performance of the memory subsystem (L2 cache and DRAM), which is discussed in the application note "Optimizing 6x86-Based Systems Using CPUmark<sub>16</sub> TM."

## Initial Board and BIOS Verification Using PUZZLE.EXE

#### Notes:

- 1. Set jumpers on system board and select BIOS options appropriately:

- a) Set CPU bus clock (CLK signal) to frequency specified for CPU:

- 50 MHz for 6x86 50/100, 60 MHz for 6x86 60/120, ...

- b) Set processor core/bus frequency ratio (CLKMUL signal) to 2X

- c) Set L1 write policy (WB/WT# signal) to WRITE-BACK

- d) ENABLE instruction pipelining (NA# signal)

In most cases, once a system is set up for Pentium, the only jumper change needed is the bus frequency (item "a"). In cases where the Pentium uses a 3/2 clock ratio the appropriate jumper must also be changed (item "b"). Items "c" and "d" are usually not selectable with jumpers but may be options in BIOS.

- 2. Other factors besides pin assignments can cause problems with the system boot. Be sure that the bus frequency, CPU voltage, selectable wait states and other parameters are within specifications. Whenever possible, be conservative with jumper and BIOS settings until the system boots successfully and only then try to enhance system performance by changing these settings. For instance, change the 60 MHz bus to 50 MHz if you think the motherboard may be having problems at the higher frequency.

- 3. Enable L1 cache in WRITE-BACK mode. To do this, re-boot the system, enter the BIOS screen and enable L1 in write-back mode. An alternative method is to run M1.EXE (available from IBM Microelectronics) and do the following:

- a) Set CCR2 LOCK NW=0 and write 6x86 (PF3)

- b) Set CR0 CD=0 and CR0 NW=0 and write 6x86 (PF3)

- 4. The target score for PUZZLE is:

<u>CPU</u> <u>PUZZLE score</u> 6x86 50/100 1.09 seconds 6x86 60/120 0.88 seconds

The time can vary up to one hundredth of a second. If your time is higher, then something is wrong with the setup. The time returned from "PUZZLE" can be used as a diagnostic tool to identify the problem.

- 5. If the time is grossly slow (greater than 7.41 seconds), the L1 cache is disabled or the bus frequency is too slow. Turn the system off and make sure the jumpers for bus frequency (see note 1) are set correctly. Turn the system on and enable the L1 cache using software (see note 3).

- 6. If the time is somewhere between the target score and 7.41 seconds, the L1 cache is in write-through mode. The exact number you get is determined by the state of the L2 cache (write-back, write-through or disabled) and type of L2 cache (asynchronous or synchronous). Make sure that the WB/WT# jumper is set for write-back (see note 1) and enable the L1 cache in write-back mode (see note 3).

## **Acknowledgment**

Thanks to Michael Hyatt and Marines Sousa for their contributions to this work.

Thanks to Ross Ogilvie who wrote the original code for PUZZLE.EXE and checked his Z80 several times during the night to ensure that the 8 hour run completed without incident.

### **References**

1. IBM 6x86 Microprocessor Databook, IBM Microelectronics, 1996.

IBM Corporation 1995. All rights reserved.

IBM and the IBM logo are registered trademarks of International Business Machines Corporation. IBM Microelectronics is a trademark of the IBM Corp.

All other product and company names are trademarks/registered trademarks of their respective holders. 1995 IBM Corp.

The information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not effect or change IBM's product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All the information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for any damages arising directly or indirectly from any use of the information contained in this document.