# Advanced Micro Devices

# **Am79C82A**

### **CMOS Data Path Controller (DPC)**

### **DISTINCTIVE CHARACTERISTICS**

- Performs reception and transmission of frames

- Byte (8 + 1 bits) to word (32 + 4 bits) conversions

- Reports error status

- Performs parity check and generation

- 12.5-MHz byte clock

- 145-lead pin grid array package

- Single +5-V supply

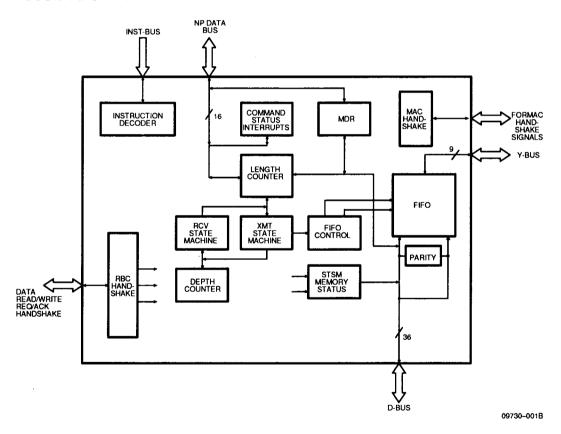

### **BLOCK DIAGRAM**

### GENERAL DESCRIPTION

The Am79C82A Data Path Controller (DPC) is a CMOS device that, along with the Am79C81A RAM Buffer Controller (RBC), performs buffer management for high-speed interfaces. It buffers and stores the received packets one after the other in Buffer Memory. It also

identifies the status of the packet, including any error conditions. This +5-V device runs at 12.5 MHz rate and allows Buffer Memory throughput of 200 Mbps. All inputs and outputs are TTL-compatible, providing a simple interface to other external devices.

### NOTE

The word "frame" is used in the SUPERNET data sheets to describe three different groups of information.

1) One group is passed over the network media and has the following structure:

| .,       |           | -       |             |         |       |             |                |           |

|----------|-----------|---------|-------------|---------|-------|-------------|----------------|-----------|

| Frame    | Start     | Frame   | Destination | Source  | Frame |             | Frame          | End       |

| Preamble | Delimiter | Control | Address     | Address | Check | Information | Check Sequence | Delimiter |

2) The others are stored in buffer memory and are structured as follows:

A) Transmit frame

| 1 |            | Frame   | Destination | Source  |             | Frame          |         |

|---|------------|---------|-------------|---------|-------------|----------------|---------|

|   | Descriptor | Control | Address     | Address | Information | Check Sequence | Pointer |

|   |            |         |             |         |             |                |         |

B) Receive frame

|            | Frame   | Destination | Source  |             | Frame          |

|------------|---------|-------------|---------|-------------|----------------|

| Descriptor | Control | Address     | Address | Information | Check Sequence |

### TABLE OF CONTENTS

| DISTINCTIVE CHARACTERISTICS                                      | 1        |

|------------------------------------------------------------------|----------|

| BLOCK DIAGRAM                                                    | 1        |

| SENERAL DESCRIPTION                                              | 2        |

| CONNECTION DIAGRAM                                               | 4        |

| PIN DESIGNATIONS                                                 | 5<br>7   |

| OGIC SYMBOL                                                      |          |

| ORDERING INFORMATION                                             | 8        |

| PIN DESCRIPTION                                                  | 9        |

| UNCTIONAL DESCRIPTION                                            | 16       |

| Functional Overview                                              | 16       |

| Transmit Mode                                                    | 16       |

| Receive Mode                                                     | 16       |

| Claim/Beacon Frame Handling                                      | 16       |

| User Test Mode                                                   | 16       |

| Overview Of User-Accessible Resources                            | 16       |

| Programmable Resources                                           | 16       |

| Hardwired Resources                                              | 17       |

| Block Diagram                                                    | 17       |

| NP — DPC Interface                                               | 18       |

| Clock Synchronization                                            | 18       |

| Instruction Set                                                  | 18       |

| Mode Register (MODE)                                             | 21       |

| System Status Register (STAT) and Interrupt Mask Register (IMSK) | 23       |

| Buffer Memory Data Organization                                  | 24       |

| Receive Frame Descriptor (Status and Length)                     | 24       |

| Transmit Frame Descriptor                                        | 27       |

| Pointer Format                                                   | 28       |

| Byte Order Within a Word                                         | 29       |

| Byte Boundary Operation                                          | 29       |

| RBC — DPC Interface                                              | 29       |

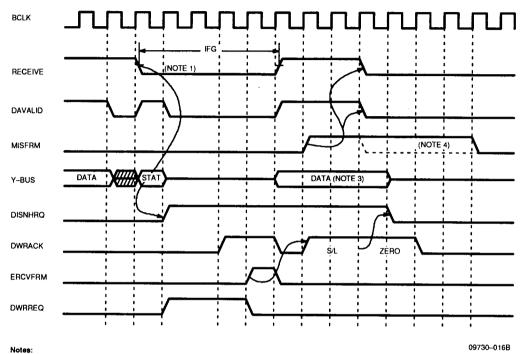

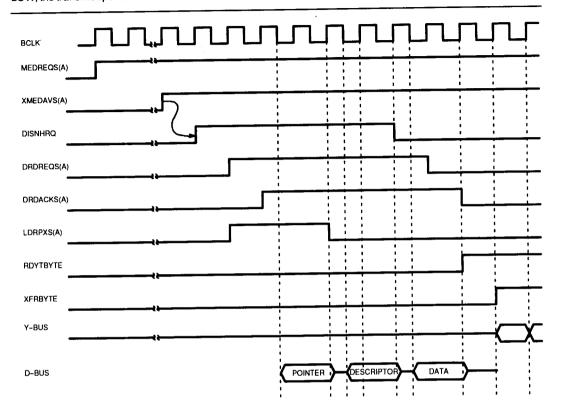

| Received Data                                                    | 29       |

| Data to be Transmitted                                           | 29       |

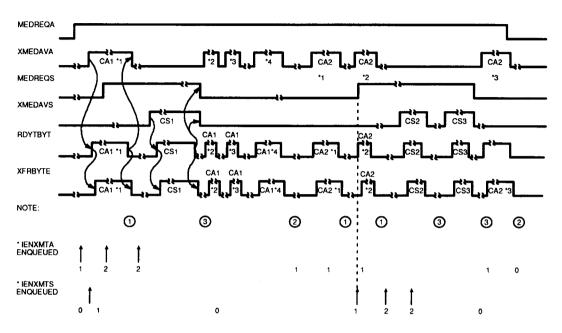

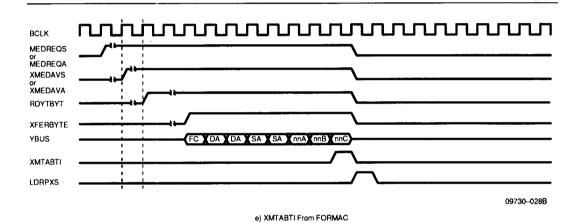

| FORMAC — DPC Interface                                           | 32       |

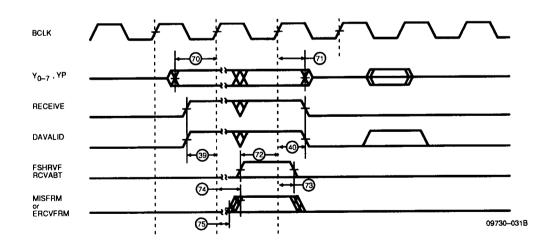

| Receive Mode                                                     | 32       |

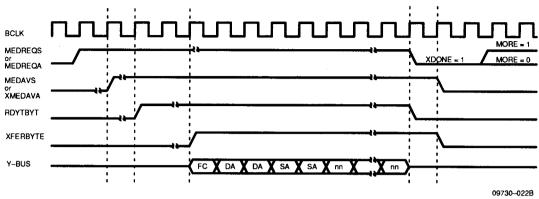

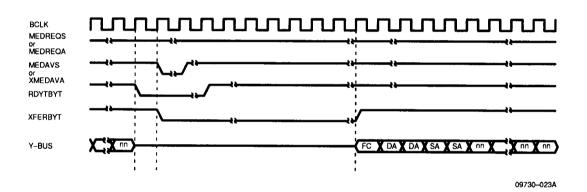

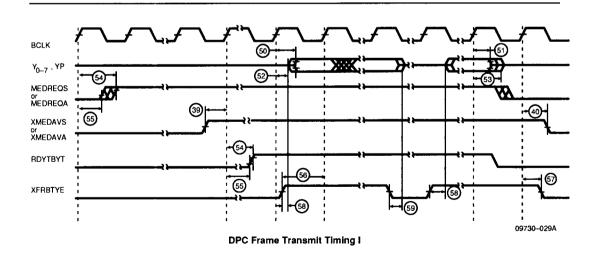

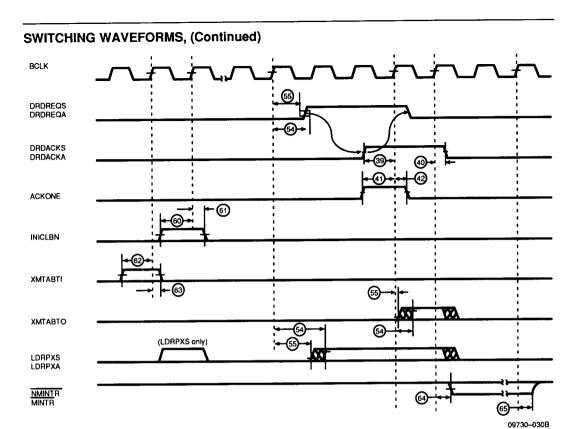

| Transmit Mode                                                    | 38       |

| ABSOLUTE MAXIMUM RATINGS                                         | 44       |

| DPERATING RANGES                                                 | 44<br>45 |

| DC CHARACTERISTICS                                               |          |

| CAPACITANCE                                                      | 45       |

| SWITCHING CHARACTERISTICS                                        | 46       |

| SWITCHING WAVEFORMS                                              | 49       |

| SWITCHING TEST CIRCUITS                                          | 56       |

| SWITCHING TEST WAVEFORMS                                         | 56       |

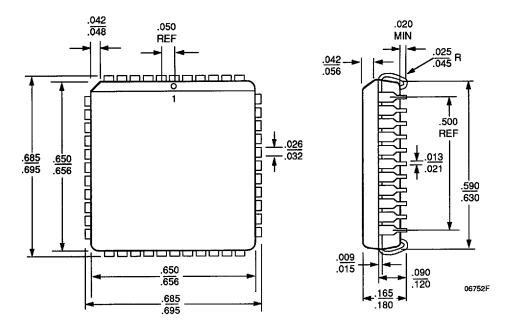

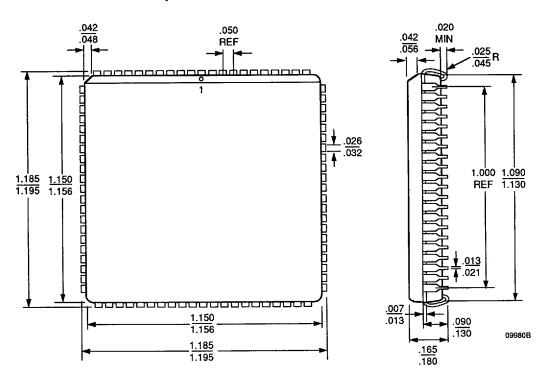

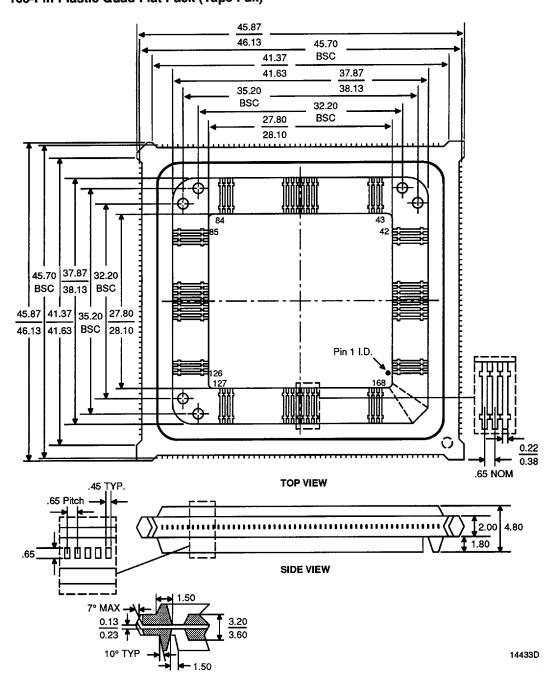

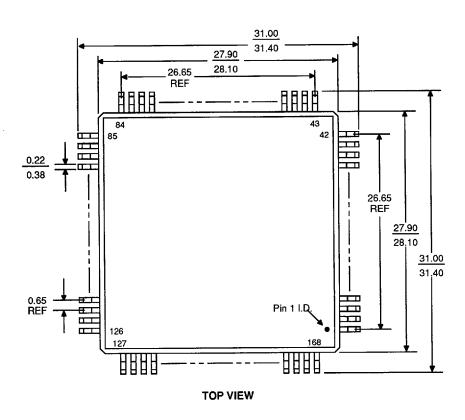

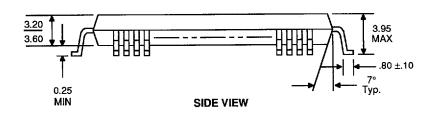

| PHYSICAL DIMENSIONS                                              | 57       |

Am79C82A 3-3

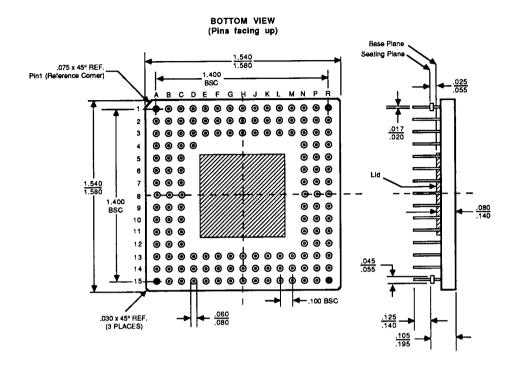

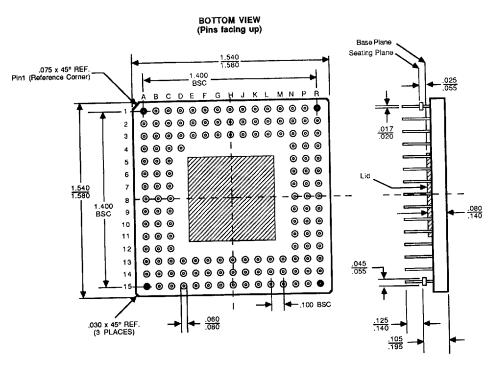

# CONNECTION DIAGRAM PGA Bottom View (pins facing up)

|     |         | В       | С       | D     | E    | F    | G      | н      | J   | ĸ   | L   | м     | N       | P         | R          |    |

|-----|---------|---------|---------|-------|------|------|--------|--------|-----|-----|-----|-------|---------|-----------|------------|----|

| ۱ [ | NC      | vcc     | CSI     | DS    | NP14 | NP11 | NP9    | NP8    | NP6 | NP3 | NP1 | NP0   | NMINTR  | RECEIVE   | ¥7         | ,  |

| 2   | NC      | INSTO   | BMODE   | NC    | NP15 | NP12 | NP10   | NC     | NP7 | NP4 | NP2 | BCLK  | vcc     | PSHRCVF   | Y6         | 2  |

| 3   | NST3    | INST2   | INST1   | READY | GND  | NP13 | GND    | NC     | vcc | NP6 | GND | MINTR | DAVALID | <b>Y4</b> | <b>Y</b> 5 | э  |

| ٠   | NC      | DRDREGA | R∕₩     | •     |      |      |        |        |     |     |     |       | GND     | <b>Y3</b> | NC         | 4  |

| 5   | DWRREO  | DRDREQ6 | RESET   |       |      |      |        |        |     |     |     |       | YP      | YI        | Y2         | 5  |

|     | LDRPXA  | BRCVFRM | GND     |       |      |      |        |        |     |     |     |       | Y0      | MEDREOS   | MEDREGA    | 6  |

| 7   | vcc     | LDRPXS  | ERCVFRM |       |      |      |        |        |     |     |     |       | vcc     | XMEDAVS   | XMEDAVA    | 7  |

| 8   | DWRACK  | GND     | GND     |       |      |      | (Botto | om Vie | w)  |     |     |       | ADYTBYT | XFRBYTE   | NC         | ۰  |

| 9   | DRDACKA | DRDACKS | PARERR  |       |      |      |        |        |     |     |     |       | GND     | XMTABTO   | XMTABTI    | ,  |

| 10  | DISNHRO | ACKONE  | MOWRACK | :     |      |      |        |        |     |     |     |       | INICLBN | RCVAST    | MISFRM     | 10 |

| 11  | MDRDACK | RBFERR  | DP2     |       |      |      |        |        |     |     |     |       | GND     | NC        | TEST       | 11 |

| 12  | DP0     | DP1     | GND     |       |      |      |        |        |     |     |     |       | SI      | so        | NC         | 12 |

| 13  | ODDPAR  | DP3     | D28     | D25   | GND  | D20  | D17    | GND    | D14 | DII | D8  | D6    | NC      | NC        | NC         | 13 |

| 14  | D31     | 030     | D27     | 024   | D22  | D19  | D16    | GND    | Dt3 | 010 | D7  | GND   | D3      | vcc       | NC         | 14 |

| 15  | vcc     | D29     | D26     | D23   | D21  | D18  | D15    | vcc    | D12 | D9  | D6  | D4    | D2      | DI        | D0         | 15 |

| 1   | ^       | 8       | с       | D     | E    | F    | G      | н      | J   | к   | L   | м     | N       | P         | R          |    |

09730-002B

# PIN DESIGNATIONS (Sorted by Pin Number)

| Pin<br>No.   | Pin Name          | Pin<br>No.   | Pin<br>Pin Name  | No.         | Pin<br>Pin Name | No.  | Pin Name       |

|--------------|-------------------|--------------|------------------|-------------|-----------------|------|----------------|

|              | NO                | 0.7          | ERCVFRM          | H-13        | GND             | N-10 | INICLBN        |

| A-1          | NC<br>NC          | C-7<br>C-8   | GND              | H-14        | GND             | N-11 | GND            |

| A-2          | NC<br>INST₃       | C-9          | PARERR           | H-15        | Vcc             | N-12 | SI             |

| A-3          | NC                | C-10         | MDWRACK          | n-13<br>J-1 | NP6             | N-13 | NC             |

| A-4<br>A-5   | DWRREQ            | C-10<br>C-11 | DP <sub>2</sub>  | J-2         | NP <sub>7</sub> | N-14 | D <sub>3</sub> |

| A-6          | LDRPXA            | C-12         | GND              | J-3         | Vcc             | N-15 | D <sub>2</sub> |

| A-7          | Vcc               | C-12         | D 28             | J-13        | D <sub>14</sub> | P-1  | RECEIVE        |

| A-7<br>A-8   | DWRACK            | C-14         | D 28             | J-14        | D13             | P–2  | FSHRCVF        |

| A-9          | DRDACKA           | C-15         | D 26             | J-15        | D <sub>12</sub> | P-3  | Y4             |

| A-3<br>A-10  | DISNHRQ           | D-1          | DS<br>DS         | K-1         | NP <sub>3</sub> | P-4  | Yз             |

|              | MDRDACK           | D-2          | NC               | K-2         | NP4             | P5   | Y1             |

| A-11         | DP0               | D-2<br>D-3   | READY            | K-2<br>K-3  | NPs             | P-6  | MEDREQS        |

| A-12         | ODDPAR            | D-3<br>D-4   | GUIDE PIN        | K-13        | D <sub>11</sub> | P-7  | XMEDAVS        |

| A-13         | D 31              | D-4<br>D-13  | D 25             | K-13        | D10             | P-8  | XFRBYTE        |

| A-14         | Vcc               | D-13<br>D-14 | D 25             | K-15        | D <sub>10</sub> | P-9  | XMTABTO        |

| A-15<br>B-1  | Vcc               | D-14<br>D-15 | D 23             | L-1         | NP1             | P-10 | RCVABT         |

| B-2          | INST <sub>0</sub> | D-13<br>E-1  | NP14             | L-1<br>L-2  | NP2             | P-11 | NC             |

| B-3          | INST <sub>2</sub> | E-2          | NP <sub>15</sub> | L-3         | GND             | P-12 | so             |

| B–3<br>B–4   | DRDREQA           | E-3          | GND              | L-13        | D <sub>8</sub>  | P-13 | NC             |

| B-5          | DRDREQS           | E-13         | GND              | L-14        | D7              | P-14 | Vcc            |

| B-6          | BRCVFRM           | E-14         | D 22             | L-15        | D <sub>6</sub>  | P-15 | D <sub>1</sub> |

| B-7          | LDRPXS            | E-15         | D 21             | M-1         | NPo             | R-1  | Y7             |

| B-8          | GND               | F-1          | NP11             | M-2         | BCLK            | R-2  | Y6             |

| B-9          | DRDACKS           | F–2          | NP <sub>12</sub> | M-3         | MINTR           | R-3  | Y5             |

| B-10         | ACKONE            | F-3          | NP <sub>13</sub> | M-13        | Ds              | R-4  | NC             |

| B-10<br>B-11 | RBFERR            | F-13         | D 20             | M-14        | GND             | R-5  | Y2             |

| B-12         | DP <sub>1</sub>   | F-14         | D 19             | M-15        | D4              | R-6  | MEDREQA        |

| B-13         | DP3               | F-15         | D 18             | N-1         | NMINTR          | R-7  | XMEDAVA        |

| B-14         | D 30              | G-1          | NP9              | N-2         | Vcc             | R-8  | NC             |

| B-15         | D 29              | G-2          | NP10             | N-3         | DAVALID         | R-9  | XMTABTI        |

| C-1          | CSI               | G-3          | GND              | N-4         | GND             | R-10 | MISFRM         |

| C-2          | BMODE             | G-13         | D 17             | N-5         | YP              | R-11 | TEST           |

|              | INST <sub>1</sub> | G-13<br>G-14 | D 17             | N-6         | Y <sub>0</sub>  | R-12 | NC             |

| C-3<br>C-4   | INST1<br>R∕W      | G-14<br>G-15 | D 15             | N-7         | Vcc             | R-13 | NC             |

|              |                   |              | NP8              | N-8         | RDYTBYT         | R-14 | NC             |

| C-5          | RESET             | H–1          |                  |             | GND             | R-15 | D <sub>0</sub> |

| C-6          | GND               | H-2          | NC<br>NC         | N-9         | GND             | n-13 | D0             |

|              |                   | H–3          | NC               |             |                 |      |                |

### PIN DESIGNATIONS

### (Sorted by Pin Name)

| Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name          | Pin<br>No. | Pin Name         | Pin<br>No. | Pin Name       |

|------------|-----------------|------------|-------------------|------------|------------------|------------|----------------|

| B-10       | ACKONE          | A-14       | D31               | B7         | LDRPXS           | A-15       | Vcc            |

| M-2        | BCLK            | N-3        | DAVALID           | A-11       | MDRDACK          | A-7        | Vcc            |

| C-2        | BMODE           | A-10       | DISNHRQ           | C-10       | MDWRACK          | B-1        | Vcc            |

| B6         | BRCVFRM         | A-12       | DPo               | R-6        | MEDREQA          | H-15       | Vcc            |

| C-1        | <del>cs</del> i | B-12       | DP <sub>1</sub>   | P-6        | MEDREQS          | J–3        | Vcc            |

| R-15       | D o             | C-11       | DP <sub>2</sub>   | M-3        | MINTR            | N-2        | Vcc            |

| P-15       | D 1             | B-13       | DP <sub>3</sub>   | R-10       | MISFRM           | N-7        | Vcc            |

| N-15       | D 2             | A-9        | DRDACKA           | N-1        | NMINTR           | P-14       | Vcc            |

| N-14       | D 3             | B-9        | DRDACKS           | M-1        | NP <sub>0</sub>  | P-8        | XFRBYTE        |

| M-15       | D 4             | B-4        | DRDREQA           | L-1        | NP1              | R-7        | <b>XMEDAVA</b> |

| M-13       | D 5             | B-5        | DRDREQS           | L-2        | NP <sub>2</sub>  | P-7        | <b>XMEDAVS</b> |

| L-15       | D 6             | D-1        | DS                | K-1        | NP <sub>3</sub>  | R-9        | XMTABTI        |

| L-14       | D 7             | A8         | DWRACK            | K-2        | NP4              | P-9        | XMTABTO        |

| L-13       | D s             | A-5        | DWRREQ            | K-3        | NP5              | N6         | Yo             |

| K-15       | Dэ              | C-7        | ERCVFRM           | J-1        | NP6              | P-5        | <b>Y</b> 1     |

| K-14       | D 10            | P-2        | <b>FSHRCVF</b>    | J2         | NP <sub>7</sub>  | R-5        | Y <sub>2</sub> |

| K-13       | D 11            | B-8        | GND               | H-1        | NP8              | P4         | Y3             |

| J-15       | D 12            | C-12       | GND               | G-1        | NP9              | P-3        | Y4             |

| J-14       | D 13            | C6         | GND               | G-2        | NP10             | R-3        | Y5             |

| J-13       | D 14            | C-8        | GND               | F-1        | NP11             | R-2        | Y6             |

| G-15       | D 15            | E-13       | GND               | F-2        | NP <sub>12</sub> | R-1        | <b>Y</b> 7     |

| G-14       | D 16            | E-3        | GND               | F-3        | NP13             | N-5        | YP             |

| G-13       | D 17            | G-3        | GND               | E-1        | NP14             | A-1        | NC             |

| F-15       | D 18            | H-13       | GND               | E-2        | NP15             | A–2        | NC             |

| F-14       | D 19            | H-14       | GND               | A-13       | ODDPAR           | A-4        | NC             |

| F-13       | D 20            | L-3        | GND               | C-9        | PARERR           | D-2        | NC             |

| E-15       | D 21            | M-14       | GND               | C-4        | ₽∕W              | H-2        | NC             |

| E-14       | D 22            | N-11       | GND               | B-11       | RBFERR           | H-3        | NC             |

| D-15       | D 23            | N-4        | GND               | P-10       | RCVABT           | N-13       | NC             |

| D-14       | D 24            | N-9        | GND               | N–8        | RDYTBYT          | P-11       | NC             |

| D-13       | D 25            | D-4        | GUIDE PIN         | D-3        | READY            | P-13       | NC             |

| C-15       | D 26            | N-10       | INICLBN           | P-1        | RECEIVE          | R-12       | NC             |

| C-14       | D 27            | B-2        | INST <sub>0</sub> | C-5        | RESET            | R–13       | NC             |

| C-13       | D 28            | C-3        | INST <sub>1</sub> | N-12       | SI               | R-14       | NC             |

| B-15       | D 29            | B-3        | INST <sub>2</sub> | P-12       | so               | R-4        | NC             |

| B-14       | D 30            | A-3        | INST3             | R-11       | TEST             | R–8        | NC             |

|            |                 | A-6        | LDRPXA            |            |                  |            |                |

Am79C82A

### LOGIC SYMBOL

09730-003B

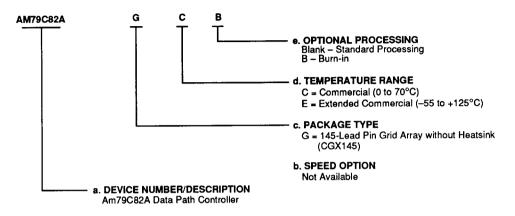

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of:

a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Com | nbinations          |

|-----------|---------------------|

| AM79C82A  | GC, GCB, GE,<br>GEB |

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

### PIN DESCRIPTION

### **Buffer Memory Interface**

### D<sub>0-31</sub>

### Data Bus (Input/Output; Three State)

The D-bus interfaces the DPC to the Buffer Memory or any external logic. These lines are outputs whenever the DPC writes frame data, status and length, or a zero field into the memory. When not actively driving out, these pins are always in the input mode. The DPC uses input data from the Buffer Memory for frame transmission when DRDACK is HIGH.

### DP<sub>0-3</sub>

### D-bus Parity (Input/Output; Three State)

The DP-bus contains the parity bits for the D-bus. DPo contains parity for Do-7, DP1 for De-15, DP2 for D16-23, and DP3 for D24-31. The parity can be either even or odd based on the state of the ODDPAR pin. No parity provision is provided for the data on the NP-bus. When the MSYPAR bit in the mode register is LOW, then no parity is used in the system and the DP lines are never outputs.

When MSYPAR is HIGH, then the FORMAC, the Host, the NP, and the Buffer Memory have parity. In this case, the DP lines are outputs whenever a received frame, its status and length, or a zero field are being written. Internally the parity logic just checks the parity when the frame is stored; it generates parity for status and length and the zero field. Otherwise these lines are inputs, and the parity is just checked for correctness when either an NP or Host read or write request is serviced.

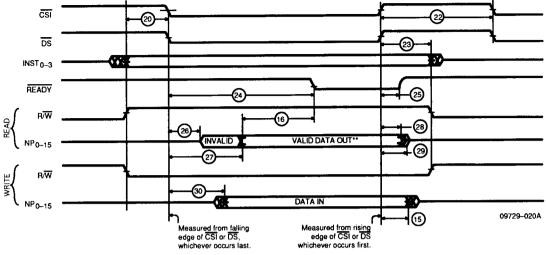

### Node Processor (NP) Interface

#### **BMODE**

### **Bus Mode (Input; Active HIGH)**

BMODE indicates that the NP is operating synchronously with the DPC. In asynchronous operation, BMODE is LOW. BMODE should be used as a strapping pin. This pin only affects the handshake on the NP-bus, DS, CSI, and READY lines.

### **CSI**

### Chip Select Input (Input; Active LOW)

The CSI LOW indicates that the NP has selected the DPC to execute an instruction. Internal execution of instructions is only enabled if CSI and DS are both LOW. CSI and DS are ANDed internal to the RBC.

When  $\overline{CSI}$  is HIGH, the INST<sub>0-3</sub> and R/ $\overline{W}$  lines are ignored and the NP-bus is kept in the three-state mode.

### DS

### Data Strobe (Input; Active LOW)

The  $\overline{DS}$  signal, together with  $\overline{CSI}$ , acts as an instruction enable when the NP is synchronous to the BCLK as specified by BMODE pin being HIGH.  $\overline{CSI}$  and  $\overline{DS}$  are ANDed internal to the RBC.

$\overline{DS}$  is used for defining the presence of data on the NP-bus when the NP is asynchronous to the BCLK (as specified by BMODE being LOW). In this case,  $\overline{DS}$  behaves much like the data strobes on slave devices connected to standard microprocessors. When  $R/\overline{W}$  and  $\overline{CSI}$  are LOW, a write operation is in progress from the NP to the DPC on the NP-bus, and  $\overline{DS}$  should become LOW whenever the data to be written is valid. It should stay active and the data on the NP-bus should stay valid until the DPC takes the  $\overline{READY}$  line LOW.

In case of a read operation when R<sub>1</sub>W is HIGH and CSI is LOW, the NP makes DS go LOW whenever it is ready to accept the read data. Subsequently, the DPC provides valid data and also asserts READY LOW. After this, the NP can take DS HIGH any time it wants. Until it does so, the DPC provides valid data on the NP-bus as output.

### INST<sub>0-3</sub>

### instruction Lines (Inputs)

The four instruction lines provide a series of instructions to the DPC. These instructions are valid whenever  $\overline{DS}$  and  $\overline{CSI}$  are both LOW.

When the NP runs on a clock that is synchronous to the BCLK, as indicated by the BMODE pin being HIGH, the INSTo-3 lines, R/W, DS, and CSI should be active for an integral number of BCLK cycles.

When the NP runs asynchronous to the BCLK, as indicated by the BMODE pin being LOW, the INST<sub>0-3</sub> lines, R/ $\overline{W}$ ,  $\overline{DS}$ , and  $\overline{CSI}$  should be active until  $\overline{READY}$  goes LOW. A LOW state on the R/ $\overline{W}$  pin indicates a write into the DPC and a HIGH indicates a read from the DPC on the NP-bus.

### MINTR

# Maskable Interrupt (Output; Open Drain, Active LOW)

The MINTR signal is used to interrupt the NP. This signal goes LOW one BCLK cycle after an unmasked status bit gets set because of an interrupt condition. The maskable bits in the status register of the DPC may be masked out to prevent generation of this interrupt. MINTR stays LOW until the status register is read, at which time it goes HIGH. If a status bit is set during the same cycle that the status register is read, then MINTR will return LOW on the following cycle. MINTR can thus be used with either edge- or level-sensing interrupt controllers.

### **NMINTR**

# Non-Maskable Interrupts (Output; Open Drain, Active LOW)

This signal is similar to the MINTR signal except that the status bits that cause NMINTR to go LOW cannot be masked out by programming. If any of these selected

status bits are set, then NMINTR will go LOW on the following BCLK cycle and will stay LOW until the NP reads the status register. The status bits are then cleared unless the bit is being set at the same time that the status register is being read. Following a status register read, NMINTR will return HIGH. If another status bit was set on the same cycle as the status register was read, then NMINTR will return LOW on the following BCLK cycle.

### NP<sub>0-15</sub>

### Node Processor Bus (Input/Output; Three State)

The NP-bus carries the data for initializing and reading or writing the various registers in the DPC. The use of this bus by the NP for reading or writing does not depend on the activity on the Y-bus or the D-bus.

The NP-bus lines are outputs whenever a read instruction is provided to the DPC by the NP using the instruction lines. This condition is signified by  $R/\overline{W}, \overline{CSI},$  and  $\overline{DS}$  being active. The NP-bus is three-stated if the  $\overline{DS}$  or  $\overline{CSI}$  lines become inactive. Note that the instruction lines,  $\overline{CSI}$  and  $\overline{DS}$  can all be asynchronous with respect to the BCLK, and hence the duration the NP-bus as an output is independent of BCLK when the BMODE pin is LOW.

### READY

### Ready Line (Output; Open Drain, Active LOW)

The READY signal is a handshake signal for use with an asynchronous NP. When the BMODE pin is HIGH, READY is also HIGH and is typically not used in the system. When BMODE is LOW, the NP runs asynchronous to the BCLK; READY indicates when the instruction is acted upon. In case of a write instruction, READY goes LOW after the data is clocked into the DPC. In case of a read instruction, READY goes LOW after the DPC supplies valid data on the NP-bus.

### R/W

### Read/Write (Input)

When  $R/\overline{W}$  is LOW, data is written into one of the RBC's registers or an instruction is executed. When  $R/\overline{W}$  is HIGH, data is read from an RBC register onto the NP-bus.  $R/\overline{W}$  should be controlled in the same manner that INST<sub>0-3</sub> are.

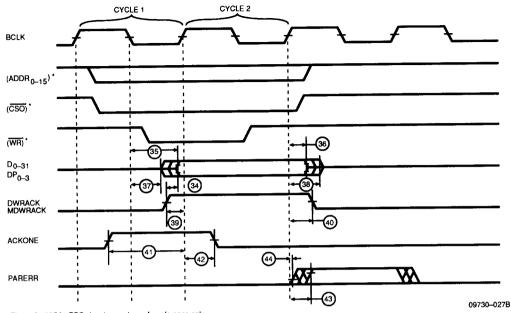

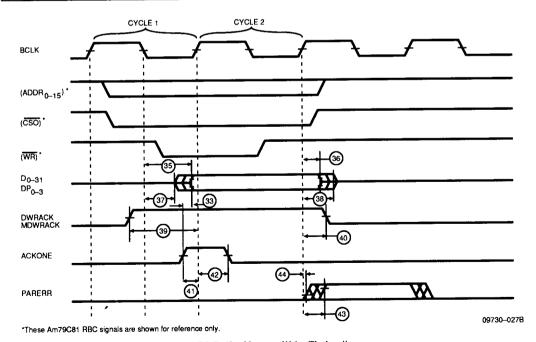

# RAM Buffer Controller (RBC) Interface ACKONE

### Acknowledge First Cycle (Input; Active HIGH)

The ACKONE signal, generated by the RBC, indicates that the current clock cycle is the first half of a two-cycle memory transfer. The DPC uses this in conjunction with

the DWRACK signal to generate the proper timing to drive the Do-31 and DPo-3 pins.

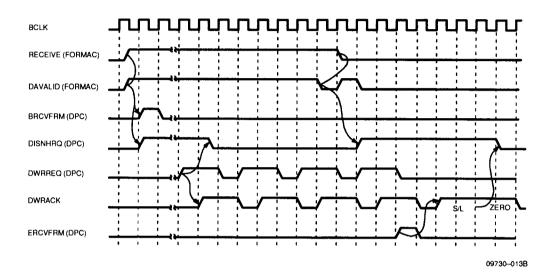

### **BRCVFRM**

### Beginning of Received Frame (Output; Active HIGH)

BRCVFRM indicates to the RBC that the following DWRREQ is a request for the first long word of the received frame. BRCVFRM is asserted for one clock cycle and is synchronous with BCLK. BRCVFRM becomes HIGH one cycle after the DPC begins receiving a frame (RECEIVE and DAVALID become HIGH).

### DISNHRQ

## Disable Node, Host Processor Request (Output; Active HIGH)

DISNHRQ is asserted by the DPC to indicate to the RBC that the DPC requests a continuous access of memory. DISNHRQ becomes HIGH to guarantee that the DPC will get an acknowledgment within one BCLK after it requested to read from or to write into memory. DISNHRQ is given to avoid the overflow of internal FIFO, to keep inter-frame gap short between two frames during reception, and to improve speed of transmission.

DISNHRQ is a level signal and is synchronous with BCLK. During receive, DISNHRQ becomes HIGH at the beginning of a receiving frame, and also at the end of the receiving frame to allow the DPC to write status-length and zero field into memory. During transmit, DISNHRQ can become HIGH for various reasons, such as when the DPC processes a descriptor or a pointer to locate the next frame in a chained transmit mode.

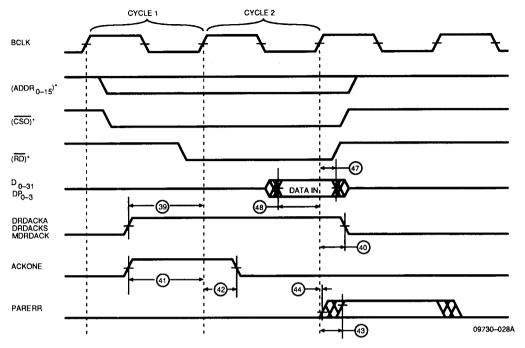

### **DRDACKA**

### DPC Read Acknowledge A-frame (Input; Active HIGH)

DRDACKA is an RBC handshake response to the DPC read request DRDREQA. DRDACKA going HIGH allows the DPC to read a long word from the D-bus into the DPC internal FIFO. The RBC will only generate DRDACKA in response to DRDREQA.

#### DRDACKS

### DPC Read Acknowledgment S-frame (Input; Active HIGH)

The DRDACKS is an RBC handshake response to the DPC read request DRDREQS. Each DRDACKS signal is synchronous with BCLK and lasts for two BCLKs. The RBC generates this acknowledge in response to DRDREQS within two BCLK cycles since this request gets highest priority. When DRDACKS becomes HIGH, the DPC assumes that a 32-bit long word is ready on the D-bus. The DPC takes DRDREQS LOW and receives data from the D-bus into its internal FIFO. The RBC will

3-10 Am79C82A

not generate DRDACKS unless the DPC requests a read of memory for transmitting an S-frame, using DRDREQS.

### DRDREGA

# DPC Read Request For A-frame (Output; Active HIGH)

The DRDREQA signal is asserted by the DPC to request from the RBC a DMA address for reading a long word of an A-frame into the DPC internal FIFO. DRDREQA goes HIGH only when the DPC transmits A-frames, the MEDREQA and XMEDAVA are HIGH, and when the DPC needs to fill up its internal FIFO with A-frame data to guarantee continuity of frames transmitted. The DPC guarantees that DRDREQS, DRDREQA, and DWRREQ are never HIGH simultaneously.

### DRDREQS

# DPC Read Request For S-frame (Output; Active HIGH)

The DRDREQS signal is asserted by the DPC to the RBC to request a DMA address for reading a long word (32-bit D-bus) of S-frame data from memory into the DPC internal FIFO. The RBC responds to this by asserting DRDACKS whenever its address output points to the right memory location. The DRDREQS is a level signal synchronous to BCLK. It goes HIGH only whenever the DPC transmits S-frames (MEDREQS and XMEDAVS are HIGH), and when the DPC needs to fill up its internal FIFO with S-frame data to guarantee continuity of frames transmitted.

DRDREQS will not become HIGH when either DRDREQA or DWRREQ are HIGH.

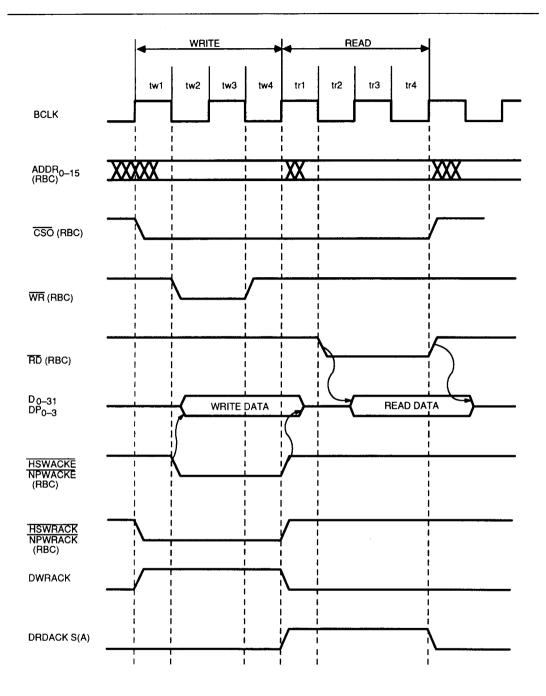

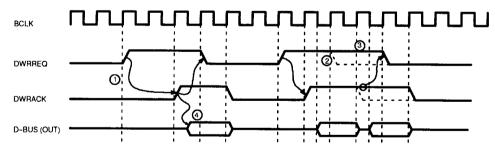

### **DWRACK**

### DPC Write Acknowledge (Input; Active HIGH)

DWRACK is the RBC handshake response to the DPC write request DWRREQ going HIGH. DWRACK is a signal synchronous with BCLK, and lasts for multiples of two clock cycles. When DWRACK goes HIGH, the DPC assumes that the address on the RBC address bus is valid. The DPC enables data from its FIFO onto the Dbus. For each DWRREQ, one DWRACK is generated and lasts for two clock cycles. The RBC should assert DWRACK within two clock cycles after DWRREQ becomes HIGH. The RBC will usually not generate DWRACK unless DWRREQ is HIGH. The only exception to this rule is when the DPC writes the status and length of a received frame into memory. In this case, DWRACK is generated in response to ERCVFRM and remains HIGH for four clock cycles.

### DWRREQ

### **DPC Write Request (Output; Active HIGH)**

DWRREQ is a signal from the DPC to the RBC to request a memory write cycle for the frame being received. The DPC asserts DWRREQ when it is in the receive mode and its FIFO buffer has enough data to write one long word into memory. When the DPC writes

status and length of the received frame into memory, it does not assert DWRREQ.

DWRREQ stays HIGH until the RBC asserts DWRACK. However, it will not go HIGH when DRDREQA or DRDREQS is HIGH. The DPC can keep DWRREQ HIGH or assert another DWRREQ after the previous one is serviced.

### **ERCVFRM**

### End of Received Frame (Output; Active HIGH)

The ERCVFRM signal indicates to the RBC that the received frame is ended. ERCVFRM commands the RBC to move the pointer back to the beginning of the frame so that the DPC can write frame status and length into memory. ERCVFRM is asserted one BCLK cycle after the RBC brings DWRACK HIGH to write the last few bytes of the receiving frame in the memory. ERCVFRM is synchronous with BCLK and lasts for one BCLK cycle.

### **LDRPXA**

### Load RPX For A-frame (Output; Active HIGH)

LDRPXA instructs the RBC to load data from Do-15 to the RPXA pointer. This signal is given to support the chain transmit scheme of the FDDI. This signal goes together with DRDREQA and DRDACKA and is used to load the RPXA pointer. LDRPXS and LDRPXA do not become HIGH simultaneously. LDRPXA is synchronous with the clock. It is asserted simultaneously with DRDREQA and stays asserted until two clock cycles after the DPC receives DRDACKA. LDRPXA is not asserted unless XMEDAVA is HIGH.

### **LDRPXS**

### Load RPX For S-frame (Output; Active HIGH)

The primary function of LDRPXS is to instruct the RBC to load data from  $D_0$ — $D_{15}$  to the RPXS register (or into the ACP register when in claim or beacon mode). This signal is given to support the chain transmit scheme of the FDDI. LDRPXS is synchronous with BCLK. It is asserted simultaneously with DRDREQS and stays HIGH until two clock cycles after the DPC receives DRDACKS. In primary operation, LDRPXS is not asserted unless XMEDAVS is HIGH.

The secondary function of LDRPXS is to signal the RBC that the DPC's XMTABTI signal has been asserted. In this function, LDRPXS is asserted for one clock cycle on the cycle following the assertion of the XMTABTI signal.

### **MDRDACK**

### Memory Data Register (MDR) Read Acknowledgement (Input; Active HIGH)

MDRDACK is asserted by the RBC to allow the DPC to read data from the D-bus into its MDRU and MDRL registers. The DPC also checks parity on the D-bus.

### **MDWRACK**

# Memory Data Register Write Acknowledgment (Input; Active HIGH)

MDWRACK is asserted by the RBC to allow the DPC to load data from the MDRU and MDRL registers onto the D-bus. The DPC also generates parity on the D-bus parity pins (DP0-3) if the MSYPAR bit on the mode register is set.

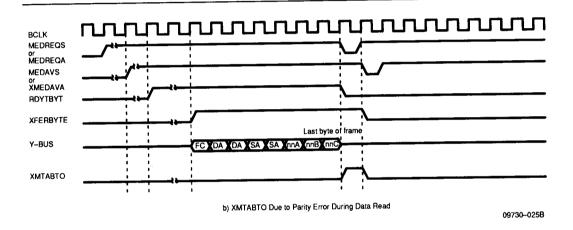

#### PARERR

### Parity Error (Output; Active HIGH)

PARERR HIGH indicates that the DPC parity checking logic has detected an error. Parity is checked on all read transfers out of the Buffer Memory. Parity is generated when the DPC writes into memory. Parity is also checked during all other writes (including DPC, NP, and Host writes) into memory. PARERR is a pulse signal, synchronous with BCLK. It lasts for one clock cycle. Parity can be even or odd depending on the state of the ODDPAR pin.

### **RBFERR**

### Receive Buffer Full Error (Input; Active HIGH)

The RBFERR signal is asserted by the RBC to indicate that the receive memory buffer is full. RBFERR is a level signal and synchronous with BCLK. When RBFERR becomes HIGH, the DPC terminates the received frame (i.e., aborts its reception and, unlike RCVABT, no status, length, or zero is written).

# Fiber Optic Ring Media Access Controller (FORMAC) Interface

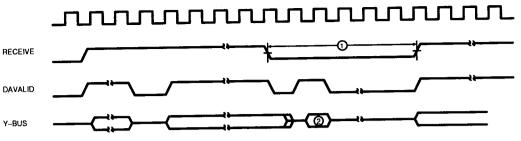

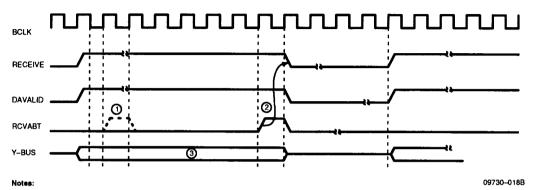

### DAVALID

### Data Valid (Input; Active HIGH)

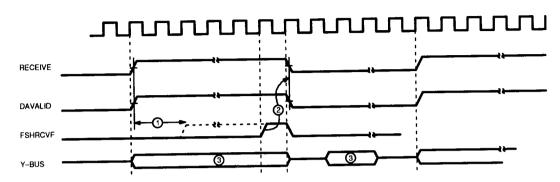

The DAVALID signal indicates that valid information is present on the Y-bus for input. If DAVALID is HIGH when RECEIVE is HIGH, the DPC inputs the data byte. DAVALID is HIGH for an integral number of BCLK cycles. Hence, if the FORMAC sends a frame in small bursts, DAVALID stays HIGH only for those cycles when the data is being sent. DAVALID can also go HIGH when RECEIVE is LOW. In this case, the value on the Y-bus is interpreted as status by the DPC and is strobed into an internal status latch. DAVALID will not go HIGH when the DPC is in the transmit mode (as indicated by XMEDAVS or XMEDAVA being HIGH).

### **FSHRCVF**

### Flush a Received Frame (Input; Active HIGH)

If FSHRCVF is HIGH when RECEIVE is HIGH, the RBC flushes the frame that the DPC is receiving. FSHRCVF can be the output of either the Am79C83 FORMAC or of external address detection logic. FSHRCVF should be LOW during receive for the DPC to accept the frame. FSHRCVF should not become HIGH when the DPC is

not receiving. The FORMAC is designed so that FSHRCVF cannot go HIGH in the same cycle in which RECEIVE goes HIGH, and it can only go HIGH when RECEIVE is HIGH.

### INICLBN

### Initialize Claim and Beacon (Input; Active HiGH)

The INICLBN signal is asserted by the FORMAC to indicate that the node is in a claim or beacon mode. In this mode, the DPC resets its transmit state machine and asserts a MEDREQS to the FORMAC. This pin is used to support FDDI claim and beacon functions.

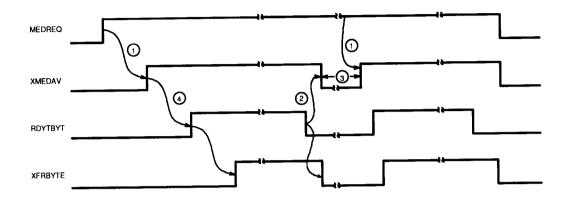

### **MEDREQA**

### Media Request For A-frame Transmit (Output; Active HIGH)

The MEDREQA signal is asserted by the DPC to indicate to the FORMAC that A-frame data is waiting to be transmitted. The FORMAC responds by asserting XMEDAVA whenever it gains access to the medium for transmission. The DPC asserts it whenever the NP gives DPC an instruction to transmit an A-frame chain segment (IENMXTA). A second IENXMTA will queue up a second chain segment and will cause the DPC to assert MEDREQA again. This keeps MEDREQA HIGH when the end of the first chain segment is reached. MEDREQA goes LOW if a transmit abort occurs.

The NP can abort any queued-up frames by issuing an IABTXMT instruction. The FORMAC can also abort a frame by de-asserting XMEDAVA during a transmit. The FORMAC will not generate XMEDAVA unless the DPC requests (using MEDREQA) the medium to transmit A-frames. The FORMAC also will not generate XMEDAVS and XMEDAVA simultaneously.

### **MEDREQS**

### Media Request for S-frame Transmit (Output; Active HIGH)

The MEDREQS signal is asserted by the DPC to indicate to the FORMAC that S-frame data is waiting to be transmitted. The FORMAC responds by asserting XMEDAVS whenever it gains access to the medium for transmission. The DPC asserts it whenever the NP gives DPC an instruction to transmit an S-frame chain segment (IENMXTS). A second IENXMTS will queue up a second chain segment and cause the DPC to assert MEDREQS again. This keeps MEDREQS HIGH when the end of the first chain segment is reached. MEDREQS goes LOW if a transmit abort occurs.

The NP can abort any queued-up frames by issuing an IABTXMT instruction. The FORMAC can also abort a frame by deasserting XMEDAVS during a transmit. The FORMAC will not generate XMEDAVS unless the DPC requests (using MEDREQS) the medium to transmit an S-frame.

### **MISFRM**

### Missed Frame (Output; Active HIGH)

MISFRM is asserted by the DPC to indicate to the FOR-MAC that the DPC missed an incoming frame. MISFRM is synchronous with the system clock, and is asserted when the DPC cannot enter a received frame into its FIFO. This is caused by the inter-frame gap between two received frames being too short or when receive lock is set by a reset.

### **RCVABT**

### Receive Abort (Input; Active HIGH)

The RCVABT signal provides a method for the FOR-MAC to abort a frame that is being received. RCVABT should be synchronous with BCLK, and can be HIGH for one or more clock cycles. If RCVABT goes HIGH for one or more cycles when a frame is being received, the frame is aborted. Subsequent frames are received normally if RCVABT is LOW at the time. RCVABT cannot go HIGH in the same cycle that RECEIVE goes HIGH, and it can only go HIGH with the receive envelope.

### **RDYTBYT**

### Ready to Transmit Byte (Output; Active HIGH)

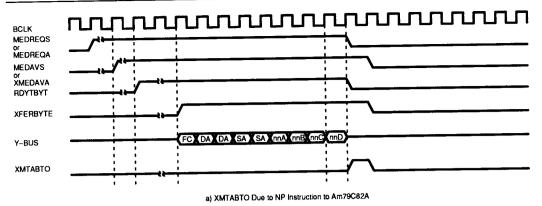

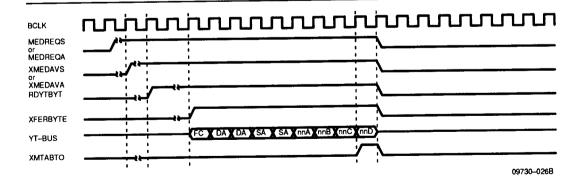

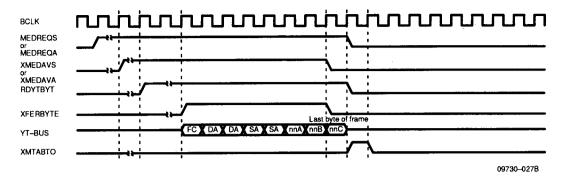

The RDYTBYT is an indication from the DPC to the FORMAC that it has filled up its internal FIFO in preparation for a frame transmission and can guarantee transmission of continuous bytes. RDYTBYT goes HIGH after the FIFO is filled in response to XMEDAVS for an Sframe or XMEDAVA for an A-frame, and other conditions for filling the FIFO are met. Normally it stays HIGH until the FORMAC reads the complete frame using the XFRBYTE signal. Then it goes LOW, signifying that it has nothing more to transmit. RDYTBYT is a level signal synchronous to BCLK. It can go LOW before the frame transmission is complete in case of an abort. If the abort is initiated by the FORMAC de-asserting XMEDAVS (or XMEDAVA), RDYTBYT (as well as MEDREQ) goes LOW in the following cycle. If the abort is initiated by the NP using an IABTXMT instruction, or by the DPC due to an error condition, the DPC conveys this information to FORMAC by de-asserting MEDREQS (or MEDREQA) and RDYTBYT. In addition, XMTABTO will go HIGH for one BCLK. RDYTBYT is never HIGH if MEDREOS or MEDREOA is LOW.

### RECEIVE

### Receive Frame (Input; Active HIGH)

The RECEIVE signal from the FORMAC indicates to the DPC that frame reception has begun. Each frame is bounded by RECEIVE. Hence, when RECEIVE goes HIGH, the DPC prepares itself for the frame coming in on the Y-bus. While RECEIVE is HIGH, DAVALID indicates whether or not the data on the Y-bus is valid. When RECEIVE goes LOW, it indicates reception for that frame is over.

RECEIVE changes state synchronous with the BCLK. After RECEIVE goes LOW, it can go HIGH again after two BCLK cycles. However, for the second frame to be stored properly, RECEIVE should go HIGH again eight

or more BCLK cycles after it goes LOW. If it goes HIGH sooner, the second frame may be ignored, because the inter-frame gap time on the network may not be sufficient for the DPC to receive this frame and store the previous one. DAVALID is used for strobing FORMAC-generated status into the DPC when RECEIVE is LOW. Typically, RECEIVE should not be HIGH when the DPC is in the transmit mode (as indicated by XMEDAVS or XMEDAVA being HIGH).

### **XFRBYTE**

### Transfer Byte (Input; Active HIGH)

The XFRBYTE signal is driven HIGH by the FORMAC in response to RDYTBYT. XFRBYTE should be synchronous to BCLK, and can be HIGH for one or more cycles at a time. Valid transmit data is impressed on the Y-bus when XFRBYTE is HIGH.

### **XMEDAVA**

### Transfer Media Available for A-frame (Input; Active HIGH)

The XMEDAVA is a FORMAC response to the DPC handshake signal MEDREQA. XMEDAVA goes HIGH when the FORMAC receives a token from the media authorizing transmission, and the FORMAC has determined that A-frames should be transmitted. The DPC then proceeds to transfer A-frame data to the FORMAC for transmission. The FORMAC will not assert XMEDAVA when MEDREQA is LOW or XMEDAVS is HIGH. It also prevents XMEDAVA and XMEDAVS going HIGH at the same time.

XMEDAVA can go LOW for a variety of reasons. During a normal A-frame transmission, the XMEDAVA goes LOW after the frame is transferred from the DPC to the FORMAC (as signified by RDYTBYT going LOW). If XMEDAVA goes LOW when RDYTBYT is still HIGH, it constitutes a transmit abort from the FORMAC to the DPC since the availability of the medium for transmitting an A-frame disappeared before the transmission was complete.

### **XMEDAVS**

### Transmit Media Available for S-frame (Input; Active HIGH)

The XMEDAVS is a FORMAC response to the DPC handshake signal MEDREQS. XMEDAVS is a level signal and is synchronous with BCLK. XMEDAVS becomes HIGH when the FORMAC receives a token from the media authorizing transmission, and the FORMAC has determined that S-frames should be transmitted. The DPC then proceeds to transfer S-frame data to the FORMAC for transmission.

XMEDAVS can go LOW for a variety of reasons. During a normal S-frame transmission, XMEDAVS goes LOW after the frame is transferred from the DPC to the FORMAC (as signified by RDYTBYT going LOW). If XMEDAVS goes LOW when RDYTBYT is still HIGH, it constitutes a transmit abort from the FORMAC to the DPC since the availability of the medium disappears before the transmission is complete. The FORMAC will not

drive XMEDAVS HIGH when either the XMEDAVA is HIGH or the DPC transmit S-frame request MEDREQS is LOW.

### **XMTABTI**

### Transmit Abort in (Input; Active HIGH)

When the XMTABTI signal is HIGH, it indicates to the DPC to abort a transmit frame. XMTABTI also causes LDRPXS to be asserted one cycle after XMTABTI is asserted. This signals the RBC that a transmit abort has occurred. S-frame and A-frame lock is also set.

### **XMTABTO**

### Transmit Abort Out (Output; Active HIGH)

When the DPC XMTABTO signal is HIGH, it indicates that the frame being transmitted was aborted for some reason (such as the IABTXMT instruction) which was detected by the DPC. The XMTABTO is not asserted in response to a XMTABTI signal assertion from the FORMAC.

Other conditions which cause XMTABTO to be asserted are:

- 1) Underflow of FIFO;

- 2) Parity error on pointer or descriptor;

- 3) Parity error on frame;

- 4) XMEDAVA(S) goes LOW prematurely; and

- 5) Coding error on pointer or descriptor.

### Y<sub>0-7</sub>

### Y-bus (Input/Output: Three State)

The Y-bus primarily carries data between the DPC and the FORMAC. It can also carry status information from the FORMAC when receiving. The Y-bus is an output whenever the DPC is transmitting and the FORMAC wants to accept the transmitted data. Hence, the DPC presents the transmit data on the Y-bus whenever the XFRBYTE input signal becomes HIGH.

The DPC uses the input data on the Y-bus only when DAVALID is HIGH. If RECEIVE and DAVALID are both HIGH, then the data on the Y-bus is interpreted as a byte in the frame. If RECEIVE is LOW and DAVALID is HIGH, then the DPC interprets the data on the Y-bus as frame-related status being sent from the FORMAC to the DPC, and stores it in a status latch. If the DPC does not receive the status field following the data bytes, then the DPC will use the previous frame's status byte for writing to memory.

### ΥP

### Y-bus Parity (Input/Output; Three State)

The YP signal indicates the parity of the Y-bus. The parity can be even or odd as specified by the ODDPAR pin. If parity is allowed, then the direction of signal flow on this pin will match that of the rest of the Y-bus (specified by the MSYPAR bit in the mode register).

### Miscellaneous

### **BCLK**

### Byte Clock (Input)

The BCLK is the main clock that runs the DPC. The bytes received by the DPC are aligned with this clock. The DPC, Buffer Memory, and FORMAC run synchronously with BCLK when the BMODE pin is strapped HIGH.

### **ODDPAR**

### Odd Parity (Input; Active HIGH)

The ODDPAR is a strappable option. When HIGH, it indicates that odd parity is in use. Odd parity is defined by this example: If byte = 00000000, correct parity bit is a "1". When the ODDPAR pin is LOW, it indicates even parity. Parity is computed on a byte basis.

### RESET

### Reset (Input; Active LOW)

This is an active-LOW hardware reset that initializes the internal state machines and the mode register in the DPC, and places them in a pre-defined state. This signal can be made active asynchronously at any point in the DPC operation and should stay LOW for at least four BCLK cycles. It can go HIGH asynchronously at any time after that.

Typically, this signal is connected to a power-on reset circuit, and possibly to a debounced reset switch. A hardware reset is necessary on startup to ensure that the DPC is in a known state and does not drive any unwanted outputs. Subsequent resets to the DPC can be software resets using the reset instruction provided in the instruction set.

Note: Instructions following a reset must wait for at least two clock cycles to be effective.

### SI

### Shift Scan Input (Input; Active HIGH)

The SI pin is input when the TEST pin is active. This pin is used to input test patterns to various internal points for incoming testing. It should be strapped LOW for normal DPC operation.

### SO

### Shift Scan Output (Output)

This pin is used for test purposes. The SO pin contains valid test-point data when TEST is HIGH. During test (test pin is HIGH), the SO pin serially shifts out the internal test points of the DPC.

### **TEST**

### Test (Input; Active HIGH)

This pin is used for test purposes and should always be connected to ground for normal operation. The TEST pin is used to force the DPC into a test mode for silicon testing. In this test mode, various internal points can be monitored on the SO pin.

### **Power Supply**

### **GND**

### **Ground (Inputs)**

There are fourteen GND pins. They must all be connected to the power return.

### $V_{cc}$

### Power (Inputs)

These are eight Vcc pins. They must all be connected to a +5–V  $\pm 5\%$  supply.

### **FUNCTIONAL DESCRIPTION**

### **Functional Overview**

#### Transmit Mode

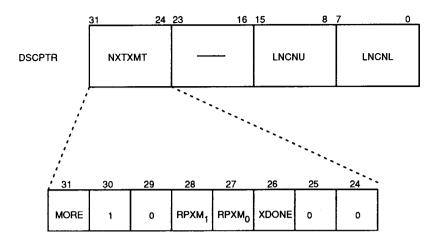

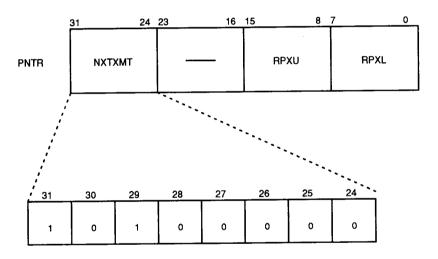

Before frames are transmitted, they are stored in Buffer Memory in a linked list of blocks that are chained together by pointers. The chain of frames to be transmitted begins with a pointer to the first block in the chain. Each block consists of a descriptor word, one or two more words of data to be transmitted, and a pointer to the next block. The descriptor contains the length of the data field in bytes plus some other information about how the data is stored. The formats of these fields are described in a later section.

The FDDI standard divides messages into two categories: 1) data that must be transmitted within a specified short period of time (S-frames), and 2) data that can tolerate a longer delay before transmission (A-frames). Each category of data is stored in the Buffer Memory in a separate, independent chain FIFO. The frames in each FIFO are chained so that each frame contains the address of the next frame in the chain.

### **Receive Mode**

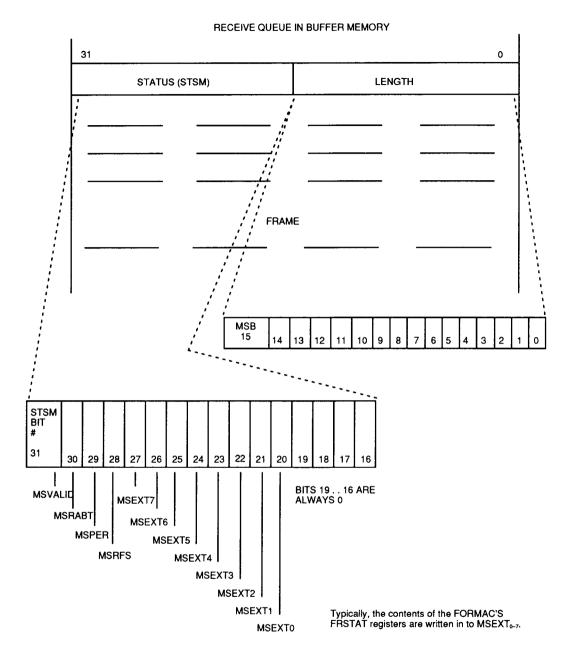

Once initialized, the DPC is ready to receive frames from the FORMAC. Frames 1 to 64K bytes long can be written into Buffer Memory using the proper request handshake with the RBC. The DPC-generated frame status and length information are normally written into memory at the start of the frame (when the RBC mode register bit MSLNSTM is set). The status bits generated by the FORMAC can also be written along with the DPC status. This scheme allows for latency of the NP in servicing received frames because the status remains stored on a per-frame basis.

All received frames are stored in Buffer Memory using a FIFO managed by the RBC. The RBC issues a "buffer full" error if a write is attempted when the FIFO is full.

### Claim/Beacon Frame Handling

The Claim and Beacon frames are specific patterns stored in the Buffer Memory. The DPC transmits these without software intervention whenever the INICLBN pin is asserted.

### **User Test Mode**

When the TEST pin is HIGH, the DPC is forced into a test mode. Registers which are not accessible from the NP-bus can be configured as a shift register and controlled by writing test patterns into the shift scan input pin (SI) and read back on the shift scan output pin (SO).

### Overview of User-Accessible Resources

### **Programmable Resources**

### Mode Register (MODE)

This register is used to program various modes of operation of the DPC. It permits received frames to be stored starting at any byte boundary within the 32-bit long word, writing either the least-significant byte first or most-significant byte first. It also allows parity checking and generation to be enabled or disabled. This register can be loaded or read using the ILDMODE or IRDMODE instructions.

### Status Register (STAT)

The status register provides an indication of various events seen by the DPC. The status bits, if not masked, can generate an interrupt to the NP. They can be read with an IRDSTAT instruction.

To assist in handling the transmission of frames, the DPC can generate interrupts under the following conditions: 1) after transmitting either individual frames or a chain of frames, 2) when all queued frames are transmitted, or 3) when the transmission is aborted for some reason.

When receiving, status is updated after each frame reception. Error conditions are also indicated by status bits. A status bit is set when the inter-frame gap is too small (i.e., the next frame comes within 6 bytes of the last one and the DPC is not ready to handle it). If the NP and the DPC simultaneously try to modify an internal register, that too is flagged. Also, a DPC internal FIFO overflow or underflow, due to some malfunction, also causes a status bit to be set.

### Interrupt Mask (IMSK)

Some of the status bits can be masked using the IMSK register bits so that the MINTR signal is not asserted. This register can be loaded or read with the ILDIMSK or IRDIMSK instructions.

#### Lenath Counter (LNCN)

The length counter (LNCN) is a 16-bit counter used to count the length of the frames being transmitted and received.

When transmit begins, the value of transmit frame length (located in memory) is loaded into the LNCN. The LNCN is decremented for each byte of data read into the internal DPC FIFO. The frame-length value specifies the number of bytes to be transmitted, starting from the location specified by the RPX of the RBC, and the byte

specified by the RPXM1 and RPXM0 bits in the transmit frame descriptor.

When receive begins, the LNCN resets itself and counts the bytes of the frame which are stored in the memory. At the end of receive frame, the contents of the LNCN are stored into memory at the beginning of the frame after the entire frame reception is complete.

The ability to read or write the LNCN (using the ILDLNCN or IRDLNCN instructions) is provided for diagnostic reasons and need not be used in normal operation.

### Memory Data Register (MDRU and MDRL)

The MDR is a 32-bit holding register in the DPC used to buffer data transferred between the NP and the Buffer Memory when RBC instructions are used rather than DMA transfers. The MDR has access to the NP-bus as well as the D-bus. The high-order 16 bits of MDR are referred to as MDRU, and the lower-order 16 bits are referred to as MDRL. The NP can load MDRU and MDRL using the ILDMDRU and ILDMDRL instructions and the NP-bus for data. These can also be read onto the NP-bus using the IRDMDRU and IRDMDRL instructions.

The contents of MDR are written into the Buffer Memory via the D-bus. The NP can read from the MDR after performing a read-memory instruction using the RBC. It can also write data into the MDR and then perform a write-memory instruction using the RBC. Data transfers take place at the location pointed to by MAR in the RBC.

The use of MDR eliminates the need for an external latching register to capture NP data, as long as the NP can tolerate the two-step access of the MDRU and MDRI

#### Instruction Set

The NP can issue software instructions to the DPC using the INST<sub>0-3</sub>, R/W, and NP<sub>0-15</sub> lines. INST<sub>0-3</sub> are normally connected to the address bus of the NP.

#### Frame Descriptors in Buffer Memory

Receive frame status and length are stored in the receive frame descriptor. This 32-bit field is in the first location in Buffer Memory for a received frame.

Frames to be transmitted are stored with a 32-bit transmit frame descriptor and a 32-bit pointer (containing the address of the transmit frame descriptor for the next frame in the transmit queue). The descriptor is stored in the Buffer Memory word just before the data to be transmitted, while the pointer is stored just after the data.

### **Hardwired Resources**

Using the BMODE pin, the DPC can interface with either a synchronous or asynchronous Node Processor. When BMODE is tied HIGH, the NP clock is synchronous with the DPC clock. In this case, the  $\overline{DS}$  and  $\overline{CSI}$  pins can be connected together and become LOW when the NP is-

sues an instruction to the DPC. When BMODE is tied LOW, the DPC can interface with an asynchronous NP. Here, the  $\overline{CSI}$  pin indicates the presence of an instruction from the NP instruction line, the  $\overline{DS}$  pin indicates the presence of data on the NP-bus, and the  $\overline{READY}$  line signifies that the DPC received the message from the NP

### **Block Diagram**

### **External Buses**

Three buses are used to interconnect these blocks to the outside world:

- NP-bus: A 16-bit bus used primarily by the Node Processor (NP) for initializing the DPC.

- Y-bus: An 8-bit bus connected to the FORMAC. It is used to receive parallel data from the FORMAC during frame reception, and to transmit parallel data to the FORMAC during transmission. It also has an associated parity bit.

- 3) D-bus: A 32-bit bus that goes to the Buffer Memory. The D-bus is used for writing received data into the Buffer Memory, and for reading data from the Buffer Memory during transmission. There are four optional parity bits that protect the 32-bit bus during frame transmission and reception.

### Instruction Decoder and Handshake

The instruction decoder logic decodes the NP instructions. The handshake synchronizes the instructions to the network clock when the NP runs asynchronous with the DPC.

#### Internal FIFO Buffer and Control

The RBC arbitrates between requests coming from the DPC and several other sources for the use of the memory. In order to guarantee continuity of the frames, the DPC has an internal FIFO to temporarily store small sections of the frames while the RBC is servicing either an NP or Host request. The internal FIFO buffer and control section consists of an internal FIFO 8 bytes deep and a state machine to control the FIFO. This block also performs a conversion between 8-bit and 32-bit parallel data between the Y-bus and D-bus.

### **Receive and Transmit State Machines**

The receive and transmit state machine controls frame reception and transmission. These state machines are also responsible for halting the DPC in case of fatal-error conditions, and for queuing up a transmit frame while a frame reception is taking place. This section also contains a depth counter to count the depth of the FIFO during receive and transmit. None of the buses communicate with this block.

#### **RBC Handshake**

Since the RBC arbitrates requests for memory address generation, the DPC must issue a request to the RBC for DMA use. The RBC handshake-block control performs sequential handshakes between the DPC and the RBC so that the RBC can generate addresses for both reading from and writing to the Buffer Memory.

### **FORMAC Handshake**

During transmit, the NP sets up an appropriate pointer in the RBC and gives the DPC instructions to transmit. The DPC tells the FORMAC that frames are waiting to be transmitted. The DPC then waits until the FORMAC has access to the medium. When the FORMAC receives a token, it tells the DPC to start transferring frames from the Buffer Memory for transmission. The FORMAC handshake block performs this logic handshake sequence between DPC and the FORMAC for transmission.

### **Parity Logic**

The DPC checks parity on all data read from or written to the Buffer Memory. (Note: the DPC also checks parity on all Host and NP reads and writes on the D-bus.)

Parity is organized as 1 bit per byte and may be configured as odd or even. However, when used in an FDDI application in conjunction with the FORMAC, the DPC must be configured for odd parity.

Parity is generated when the DPC writes into Buffer Memory.

### Locks

The DPC contains three locks (one for receive and two for transmit), used to effectively disable the appropriate function. Once the DPC is reset, the receive lock is activated which takes the DPC off-line for initialization purposes.

The two transmit locks are set by the following conditions:

- 1) S-frame lock:

- XMTABTI

XMEDAVS negated prematurely

Parity error on pointer or descriptor (S-frame queue)

Coding error on pointer or descriptor (S-frame queue)

A-frame lock:

Similar to the above S-frame condition but is used for the A-frame queue

All locks can be cleared by the ICLRLCK instruction.

### NP — DPC Interface

### **Clock Synchronization**

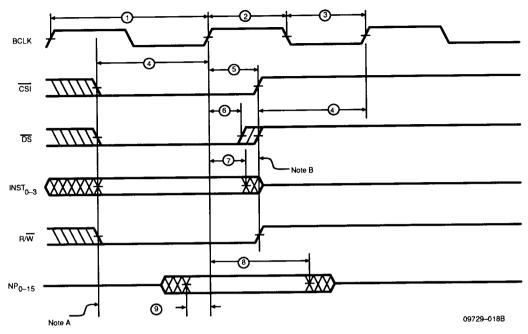

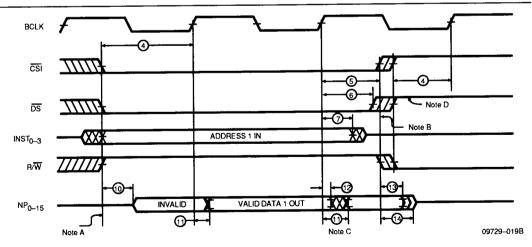

The NP can run either synchronously or asynchronously with respect to the network clock (BCLK). The BMODE pin is strapped HIGH to indicate a synchronous operation, and strapped LOW to indicate an asynchronous operation. The synchronous case can be one of two kinds.

If the NP runs on a faster clock than the DPC, there are two or more integral NP clock cycles during every DPC cycle. In this case, the NP needs to repeat instructions an integral number of times so that the instruction is active (and glitch-free) for at least one BCLK cycle.

When the NP clock is slower than BCLK, instructions have to be active and glitch-free for at least one BCLK cycle. The DPC executes the instruction only once provided  $\overline{DS}$  is LOW for only one BCLK cycle when the instructions are valid. If  $\overline{DS}$  stays LOW for several cycles, then the instruction will be executed several times.

Note that in the synchronous case, the "AND" of CSI and DS signals (complements of the CSI and DS pins, respectively) is treated as an instruction-enable signal. CSI can be asserted for multiple cycles to keep the data on the NP-bus valid for a longer duration. In the synchronous case, the READY line is LOW since it is not needed.

In the asynchronous case, a handshake convention is used (as shown in Figure 6 of the Am79C81 data sheet). The NP makes  $\overline{CSI}$  and  $\overline{DS}$  LOW to give the instruction. This is synchronized inside the DPC. This can take from two to three cycles. The DPC executes this instruction once, and at the end of the execution,  $\overline{READY}$  is driven LOW. For a load instruction,  $\overline{READY}$  is driven LOW after the data is loaded into an internal register or the instruction is executed. For a read instruction, the read data is latched and provided continuously on the NP-bus when  $\overline{CSI}$  and  $\overline{DS}$  are LOW. When the NP is done with the instruction, it de-asserts  $\overline{CSI}$  and/or  $\overline{DS}$ . This causes  $\overline{READY}$  to become HIGH and complete one instruction operation. If the handshake is violated, the results are undefined.

### Instruction Set

The instructions for the DPC are shown in Table 1. During loads, the value on NP<sub>0-15</sub> is loaded into the register; during reads, the value in the addressed register is enabled onto the bidirectional NP<sub>0-15</sub> bus.

Most of these instructions are very straightforward and need no description. Some others are described below (by instruction number order): IRESET (00 Hex). The software reset (IRESET) is the software equivalent of the hardware reset pin (RESET) and it resets the DPC. During the reset operation, all state machines are initialized, status is cleared, interrupt mask (IMSK) is activated, and the mode register is cleared. The clearing of the STAT and setting of the IMSK instructions ensures at reset that the MINTR and NMINTR lines are HIGH. The reset also clears all transmit queues for pending frames. After a reset, wait for two clock cycles before attempting another instruction.

ILDLNCN (01 Hex). Used to load a 16-bit value into the length counter. In normal operation this function is not necessary since the DPC reads the frame length from the transmit chain in the Buffer Memory. It is used for diagnostics only.

IABTXMT (08 Hex) (Instruction to Abort Transmit). If an IABTXMT is given when a frame transmission is in progress, this transmission is aborted. This is indicated by RDYTBYT, MEDREQS, and MEDREQA going LOW. XMTABTO will also go HIGH for one BCLK. If given before frame transmission is begun, all queued-up transmit chain queues (for A-frames and S-frames) are aborted and both MEDREQS and MEDREQA go LOW. When a transmit is aborted, the SXMTABT status is set. This command cannot be used to abort a Claim or Beacon frame.

IENXMTS (09 Hex) (Instruction to Enable Transmit S-frame). When the IENXMTS instruction is given to the DPC, the DPC asserts the MEDREQS signal going to the FORMAC, and waits for a XMEDAVS to come back. The NP should set up the frames to be transmitted in the Buffer Memory before giving the IENXMTS instruction to the DPC. This group of frames queued up with the IENXMTS instruction is referred to as a chain segment. A chain segment is defined as a chain of frames in which the MORE bit = 1 for all frames except the last one in which MORE = 0. The MORE bit is the most-significant bit of the descriptor word.

In essence, one IENXMTS enables one chain segment. A second IENXMTS given for a second chain segment linked to the first one is also remembered. A third IENXMTS will be remembered only if all frames in the first chain segment have already been transmitted. As a result, only two chain segments can be pending at any time. There is no constraint on the number of frames in each chain segment; however, none of the frames or their linkages can be modified after an IENXMTS is given.

IENXMTA (10 Hex) (Instruction to Enable Transmit A-frames). IENXMTA functions as IENXMTS except IENXMTA makes the DPC assert MEDREQA and start transmitting A-frames when XMEDAVA is asserted by the FORMAC.

The IENXMTS and IENXMTA should be given in such a way that at any time there are at most two of each chain segment types that are unserviced.

ICLRLCK (11 Hex). This instruction is used to clear the transmit and receive locks in conjunction with NP-bus bits 0, 1, and 2. The receive lock is set by a reset (pin or instruction), and is used to disable all receive functions until the device(s) is(are) initialized completely.

The transmit locks (one for S-frames and one for A-frames) are set by any of the following conditions:

- 1) XMTABTI:

- Negation of XMEDAVA(s) when transmission is in progress;

- 3) Parity error on pointer or descriptor; or

- 4) Coding error on pointer or descriptor.

The NP-bus bits used to clear the three locks are coded as follows:

| NP-bus Bits          |   |   |   |                    |  |  |  |  |

|----------------------|---|---|---|--------------------|--|--|--|--|

| ICLRLCK 2 1 0 Action |   |   |   |                    |  |  |  |  |

| Active               | x | x | 1 | Clear S-frame lock |  |  |  |  |

| Active               | x | 1 | x | Clear A-frame lock |  |  |  |  |

| Active               | 1 | x | X | Clear receive lock |  |  |  |  |

IRDSTAT (16 Hex). IRDSTAT enables the value of the 16-bit status register onto the NP-bus (the meaning of each bit is defined in the status section). IRDSTAT also clears the status register. This autoclear obviates the need for a separate status clear instruction and prevents interlock problems. If3 a status bit is being set during this instruction, then the old value is read, but the new value is written into status by overriding the autoclear. Some of these status conditions generate a non-maskable interrupt on the NMINTR pin. The unmasked status conditions generate a maskable interrupt on MINTR. The IRDSTAT is the means by which the NP responds to these interrupts and finds out about DPC status. The autoclear works on all the bits of STAT.

IRDLNCN (17 Hex). IRDLNCN reads the value of a 16-bit length counter (LNCN) onto the NP-bus. This counter is used primarily to count the number of bytes of the frame during receive and transmit. The IRDLNCN instruction can be given one cycle after RECEIVE goes LOW (which signifies end of frame into the DPC), and results in the value of the frame length being read onto the NP-bus. During receive only, the value of the length counter appears on the NP-bus as a complementary signal. This instruction is provided for diagnostics only, and should not be used during normal operation.

All other load/read instructions are self-explanatory register loads.

| Instruction       |         |                   |                   |        | (LSB)             |                    |                                |

|-------------------|---------|-------------------|-------------------|--------|-------------------|--------------------|--------------------------------|

| Mnemonic          | R/W     | INST <sub>3</sub> | INST <sub>2</sub> | INST   | INST <sub>0</sub> | NP <sub>0-15</sub> | Function                       |

| Software Reset:   |         |                   |                   |        |                   |                    |                                |

| IRESET            | 0       | 0                 | 0                 | 0      | 0                 | XXXX               | Software Reset                 |

| Instructions to L | oad and | Read D            |                   |        |                   |                    |                                |

| ILDLNCN           | 0       | 0                 | 0                 | 0      | 1                 | wwww               | Load LNCN                      |

| ILDMODE           | 0       | 0                 | 0                 | 1      | 0                 | wwww               | Load MODE                      |

| ILDIMSK           | 0       | 0                 | 0                 | 1      | 1                 | www                | Load IMSK                      |

| ILDMDRL           | 0       | 0                 | 1                 | 1      | 0                 | www                | Load MDRL                      |

| ILDMDRU           | 0       | 0                 | 1                 | 1      | 1                 | wwww               | Load MDRU                      |

| IABTXMT           | 0       | 1                 | 0                 | 0      | 0                 | X X X X            | Abort Transmit                 |

| IENXMTS           | 0       | 1                 | 0                 | 0      | 1                 | X X X X            | Enable Transmit for S-frames   |

| IENXMTA           | Ô       | 1                 | 0                 | 1      | 0                 | X X X X            | EnableTransmit for A-frames    |

| ICLRLCK           | Ö       | 1                 | 0                 | 1      | 1                 | wwww               | Clear Locks (Receive & Transmi |

| IRDSTAT           | 1       | 0                 | 0                 | 0      | 0                 | RRRR               | Read STAT                      |

| IRDLNCN           | 1       | ō                 | Ō                 | 0      | 1                 | RRRR               | Read LNCN                      |

| IRDMODE           | 1       | ō                 | Ö                 | 1      | 0                 | RRRR               | Read MODE                      |

| IRDIMSK           | 1       | ō                 | Ō                 | 1      | 1                 | RRRR               | Read IMSK                      |

| IRDMDRL           | 1       | Ŏ                 | 1                 | 1      | 0                 | RRRR               | Read MDRL                      |

| IRDMDRU           | 1       | Ŏ                 | 1                 | 1      | 1                 | RRRR               | Read MDRU                      |

| Reserved Instruc  | tions:  |                   |                   |        |                   |                    |                                |

| IRSV1             | 0       | 0                 | 1                 | 0      | 0                 | _                  | Reserved                       |

| IRSV2             | ŏ       | ő                 | 1                 | ŏ      | 1                 |                    | Reserved                       |

| IRSV3             | ő       | 1                 | i                 | ŏ      | ó                 | _                  | Reserved                       |

| IRSV4             | Õ       | 1                 | i                 | ő      | 1                 | _                  | Reserved                       |

| IRSV5             | 0       | 1                 | i                 | 1      | ò                 | _                  | Reserved                       |

| IRSV6             | 0       | 1                 | i                 | 1      | 1                 | _                  | Reserved                       |

| IRSV7             | 1       | ò                 | i                 | ó      | ò                 |                    | Reserved                       |

| IRSV8             | 4       | ő                 | 1                 | ő      | 1                 | _                  | Reserved                       |

| IRSV9             |         | 1                 | Ö                 | ő      | Ö                 |                    | Reserved                       |

| IRSV10            | 1       | 1                 | ő                 | ő      | 1                 | _                  | Reserved                       |

|                   | 1       | 1                 | 0                 | 1      | Ö                 | _                  | Reserved                       |

| IRSV11            | 1       | 1                 | 0                 | 1      | 1                 |                    | Reserved                       |

| IRSV12            | 1       | 1                 | 1                 | ò      | Ó                 | - <del></del>      | Reserved                       |

| IRSV13            | 1       | -                 |                   | 0      | 1                 | <del></del>        | Reserved                       |

| IRSV14            | 1       | 1                 | 1                 | _      | -                 | _                  | Reserved                       |

| IRSV15<br>IRSV16  | 1       | 1<br>1            | 1<br>1            | 1<br>1 | 0<br>1            |                    | Reserved                       |

R R R R = Read data from DPC register X X X X = Don't Care

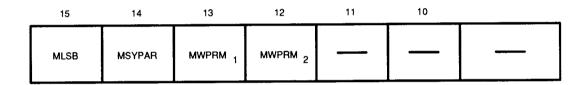

### Mode Register (MODE)

The DPC has a 4-bit mode register (MODE). The instruction ILDMODE is used to load 4-bit values from the NP-bus into MODE, and IRDMODE allows the contents of MODE to be read onto the NP-bus.

When reset (either through the RESET pin or through software IRESET), MODE is initialized so that all the bits are cleared. The NP then loads the required value into the mode register. MODE bits are shown in Figure 1 and detailed below.

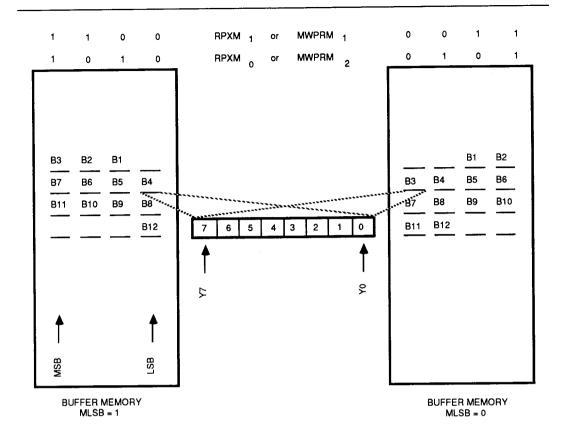

MLSB (Mode Least-Significant Byte). The MLSB HIGH indicates that the least-significant byte in the long word should be transmitted first, as shown in Figure 2. If the MLSB bit is LOW, the most-significant byte is transmitted first; however, the order of bits in a byte is not changed.

MSYPAR (Mode for System Parity Configuration). When LOW, this bit disables parity generation and checking, and the DPo-3 and YP lines are three-stated.

When MSYPAR is HIGH, parity is enabled. The parity is checked in the DPC at the D-bus for both receive and transmit. For transmit, the Buffer Memory parity is checked and carried through the DPC FIFO.

Parity is generated only when the DPC writes a received frame into memory. Parity is checked for all other transfers, including NP and Host read and write operations. Any parity error is flagged to the RBC using the PARERR pin.

MWPRM1, MWPRM2 (Mode for the WPR Byte Boundary Start). These bits indicate where to begin loading the received frame in Buffer Memory. This is shown in Figure 2. Since the frames can end on any byte of a long word, the frame may end on any boundary. The next frame is loaded at the byte boundary indicated by MWPRM1 and MWPRM2. These bits are useful for ensuring that the data unit for the next-higher layer in the protocol always begins on a long-word boundary so that byte realigning is avoided.

09730-005A

Figure 1. DPC Mode Register (MODE)

THE NUMBERS WITH A "B" PREFIX INDICATE THE ORDER IN WHICH BYTES ARE RECEIVED FROM OR TRANSMITTED TO THE MAC

09730-006A

Figure 2. Byte Ordering by MLSB

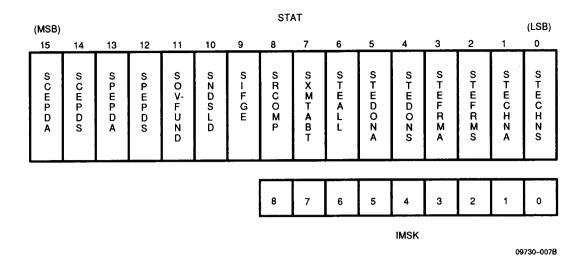

Figure 3. System Status Register (STAT) and Interrupt Mask Register (IMSK)

# System Status Register (STAT) and Interrupt Mask Register (IMSK)

The NP status logic consists of a 16-bit register (STAT) that can be read by the NP on the NP-bus. These registers accumulate system-level status. The status bits accumulate in STAT until they are read through the IRDSTAT instruction.

Some of the status bits in STAT have a mask bit which is stored in the Interrupt Mask (IMSK) register. Unless a mask bit is set, the corresponding status condition generates a maskable interrupt MINTR for these bits in STAT. A DPC reset clears all status bits and sets all the mask bits in IMSK.

### Maskable Status Bits

**STECHNS (Bit 0) (Transmit End of a Chain Segment of S-frames).** After all frames in a chain segment of an S-frame queue are transmitted out to the FORMAC, this bit is set. The NP can use this to add another chain segment to the queue. The queue supports at most two pending chain segments at any time in each FIFO.

STECHNA (Bit 1) (Transmit End of a Chain Segment of A-frames). This bit is similar to STECHNS and applies to the A-frame chain.

STEFRMS (Bit 2) (Transmit End of S-frames). This bit is set for each S-frame transmitted. If the frame happens to be the last frame in a chain segment, then the STECHNS bit will also be set.

STEFRMA (Bit 3) (Transmit End of A-frame). This bit is set for each A-frame transmitted.